Xilinx Vivado - Xilinx Vivado

| |

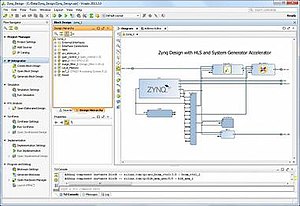

Xilinx Vivado Design Suite 2014.2 с панелью блочного дизайна (в центре) и деревом навигации по проекту (слева) | |

| Разработчики) | Xilinx |

|---|---|

| изначальный выпуск | Апрель 2012 г.[1] |

| Стабильный выпуск | |

| Написано в | C ++ |

| Операционная система | Майкрософт Виндоус, Linux |

| Доступно в | английский |

| Тип | EDA |

| Лицензия | Версия WebPACK: бесплатно для избранных (меньших) устройств[4] Другие редакции: коммерческий |

| Интернет сайт | www |

Дизайнерский люкс Vivado это программный пакет, созданный Xilinx для синтеза и анализа HDL конструкции, заменяющие Xilinx ISE с дополнительными функциями для система на чипе развитие и синтез высокого уровня.[1][5][6][7] Vivado представляет собой переработку и переосмысление всего процесса проектирования (по сравнению с ISE).[8][9][10]

Как и более поздние версии ISE, Vivado включает встроенный логический симулятор ISIM.[11] Vivado также представляет высокоуровневый синтез с набором инструментов, который преобразует код C в программируемую логику.[6]

Замена 15-летнего ISE на Vivado Design Suite заняла 1000 человеко-лет и стоила 200 миллионов долларов США.[12]

Функции

Вивадо был представлен в апреле 2012 года,[1] и представляет собой интегрированную среду проектирования (IDE) с инструментами уровня системы и IC, построенными на общей масштабируемой модели данных и общей среде отладки. Vivado включает инструменты проектирования на уровне электронных систем (ESL) для синтеза и проверки алгоритмической IP на основе C; стандартная упаковка как алгоритмического, так и RTL IP для повторного использования; сшивание IP на основе стандартов и системная интеграция всех типов системных блоков; и проверка блоков и систем.[13] Бесплатная версия WebPACK Edition Vivado предоставляет дизайнерам ограниченную версию среды проектирования.[14]

Составные части

В Синтез высокого уровня Vivado компилятор позволяет C, C ++ и SystemC программы, которые будут напрямую нацелены на устройства Xilinx без необходимости вручную создавать RTL.[15][16][17] Vivado HLS широко рассматривается для повышения продуктивности разработчиков, и подтверждено, что он поддерживает классы, шаблоны, функции и перегрузку операторов C ++.[18][16] Vivado 2014.1 представила поддержку автоматического преобразования OpenCL ядра по IP для устройств Xilinx.[19][16] Ядра OpenCL - это программы, которые выполняются на различных платформах CPU, GPU и FPGA.[16][19]

В Симулятор Вивадо является компонентом Vivado Design Suite. Это симулятор на скомпилированном языке, поддерживающий смешанные языки, Tcl скрипты, зашифрованный IP и расширенная проверка.

В IP-интегратор Vivado позволяет инженерам быстро интегрировать и настраивать IP из большой библиотеки IP Xilinx. Интегратор также настроен на MathWorks Simulink конструкции, созданные с помощью системного генератора Xilinx и высокоуровневого синтеза Vivado.[20]

В Магазин Vivado Tcl - это система сценариев для разработки надстроек к Vivado, которая может использоваться для добавления и изменения возможностей Vivado.[19] Tcl - это язык сценариев, на котором основан сам Vivado.[19] Все базовые функции Vivado можно вызывать и управлять с помощью сценариев Tcl.[19]

Поддержка устройства

Vivado поддерживает 7-ю серию Xilinx и все новые устройства (серии UltraScale и UltraScale +).[3] Для разработки, ориентированной на более старые устройства Xilinx и CLPD, уже снятые с производства Xilinx ISE должен использоваться.

Рекомендации

- ^ а б c «Xilinx Inc, форма 8-K, текущий отчет, дата подачи 25 апреля 2012 г.». secdatabase.com. Получено 6 мая, 2018.

- ^ Выпуск Vivado 2020.1, Xilinx

- ^ а б Vivado Design Suite и руководство пользователя, примечания к выпуску, установка и лицензирование, UG973 (v2020.1) 3 июня 2020 г., Xilinx

- ^ «Оценка Vivado Design Suite и WebPACK». Xilinx. нет данных. Получено 4 октября, 2020.

- ^ Моррис, Кеви (18 ноября 2014 г.). «ПЛИС начинают развиваться в центре обработки данных, Xilinx ускоряет гонку». Электронный инженерный журнал.

- ^ а б «Компания Xilinx и ее экосистема продемонстрируют все программируемые и интеллектуальные решения для зрения на ISE 2015». САН - ХОСЕ. 2015-02-04.

- ^ «Xilinx Vivado Design Suite теперь доступен в версии WebPACK». САН-ХОСЕ: Дизайн и повторное использование. 2012-12-19.

- ^ Моррис, Кевин (25 февраля 2014 г.). «Xilinx против Altera, вызывая самое большое соперничество в области полупроводников». Электронный инженерный журнал.

- ^ Дизайнерский люкс Vivado, Сайт Xilinx

- ^ Дизайнерский люкс Vivado, Первая версия выпущена в 2012 году, Загрузки Xilinx

- ^ Особенности Vivado, Xilinx

- ^ Джозелин, Луиза (2013-12-10). «Путь к успеху для стартапов eda долог и труден». Новая электроника.

- ^ EDN. "Пакет Vivado Design Suite ускоряет интеграцию и внедрение программируемых систем до 4 раз.. "15 июня, 2012. Проверено 25 июня, 2013.

- ^ Клайв Максфилд, EE Times. "Версия Xilinx Vivado Design Suite WebPACK уже доступна. "20 декабря 2012 г. Проверено 25 июня 2013 г.

- ^ Xilinx увеличивает производительность для всех программируемых SoC Zynq-7000 с помощью Vivado Design Suite 2014.3, SDK и нового руководства по методологии проектирования встраиваемых систем UltraFast, САН-ХОСЕ, 8 октября 2014 г., Дизайн и повторное использование

- ^ а б c d «Vivado Design Suite 2014.1 повышает производительность за счет автоматизации методологии проектирования UltraFast и аппаратного ускорения OpenCL». САН-ХОСЕ: Обзор рынка. 2014-04-16.

- ^ Максфилд, Клайв (26 июля 2013). "Бесплатное руководство по синтезу высокого уровня для инженеров-программистов". EE Times.

- ^ Уилсон, Ричард (27 мая 2014 г.). «Как заставить медленное программное обеспечение работать быстрее». Еженедельник электроники.

- ^ а б c d е Моррис, Кевин (2014-05-06). "Viva Vivado !, Xilinx Tunes-Up Tools". Электронный инженерный журнал.

- ^ Уилсон, Ричард (11 сентября 2013 г.). «Xilinx, MathWorks и National Instruments работают над высокоуровневым проектированием FPGA». Еженедельник электроники.