Транспьютер - Transputer

Эта статья нужны дополнительные цитаты для проверка. (Февраль 2008 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

В транспьютер это серия новаторских микропроцессоры с 1980-х годов с интегрированной памятью и последовательная связь ссылки, предназначенные для параллельные вычисления. Они были разработаны и произведены Inmos, а полупроводник компания, базирующаяся в Бристоль, объединенное Королевство.[1]

Некоторое время в конце 1980-х многие[2] считал транспьютер следующим великим проектом для вычислительной техники будущего. Хотя Inmos и транспьютер не оправдали этого ожидания, архитектура транспьютера оказала большое влияние на создание новых идей в мире. компьютерная архитектура, некоторые из которых вновь появились в различных формах в современных системах.

Фон

В начале 1980-х годов обычные центральные процессоры (CPU), похоже, достигли предела производительности. До этого времени производственные трудности ограничивали количество схем, которые можно было уместить на микросхеме. Постоянные улучшения в изготовление процесс, однако, снял это ограничение. В течение десятилетия микросхемы могут содержать больше схем, чем разработчики умели использовать. Традиционный компьютер со сложной системой команд (CISC) проекты достигли плато производительности, и не было ясно, что это может быть преодолено.[3]

Казалось, что единственный путь вперед - это увеличить использование параллелизма, использование нескольких процессоров, которые будут работать вместе для решения нескольких задач одновременно. Это зависело от того, смогут ли такие машины выполнять несколько задач одновременно, и этот процесс называется многозадачность. Как правило, это было слишком сложно для предыдущих проектов ЦП, но в более поздних разработках это было эффективно. Было ясно, что в будущем это станет особенностью всех операционные системы (ОС).

Побочным эффектом большинства многозадачных дизайнов является то, что они часто также позволяют запускать процессы на физически разных процессорах, и в этом случае это называется многопроцессорность. Недорогой ЦП, созданный для многопроцессорной обработки, может позволить повысить скорость машины за счет добавления большего количества ЦП, что потенциально намного дешевле, чем при использовании одной более быстрой конструкции ЦП.

Первые конструкции транспьютеров были созданы ученым-компьютерщиком. Дэвид Мэй и консультант по телекоммуникациям Роберт Милн. В 1990 году Мэй получил звание почетного доктора наук Саутгемптонский университет, за которым в 1991 г. последовало его избрание в качестве стипендиата Королевское общество и награждение медалью Паттерсона Институт Физики в 1992 г. Тони Фьюдж, затем ведущий инженер Inmos, был награжден Приз принца Филиппа дизайнеров в 1987 г. за работу над транспьютером T414.[4]

Дизайн

Транспьютер (название происходит от "трансистор "и" комкомпьютер"[5]) был первым микропроцессором общего назначения, разработанным специально для использования в параллельные вычисления системы. Целью было создать семейство микросхем разной мощности и стоимости, которые можно было бы соединить вместе, чтобы сформировать законченный параллельный компьютер. Название было выбрано для обозначения роли, которую будут играть отдельные транспьютеры: их количество будет использоваться в качестве основных строительных блоков, так же как транзисторы имел раньше.

Первоначально планировалось, что транспьютер будет стоить всего несколько долларов за единицу. Inmos увидела, что они используются практически для всего, от работы в качестве основного процессора компьютера до работы в качестве контроллер канала за Дисковый привод в той же машине. Запасные циклы на любом из этих транспьютеров можно было использовать для других задач, что значительно повысило общую производительность машин.

Даже один транспьютер будет иметь все схемы, необходимые для автономной работы, что обычно ассоциируется с микроконтроллеры. Цель заключалась в том, чтобы как можно проще соединять транспьютеры друг с другом, без необходимости в сложных автобус, или же материнская плата. Мощность и простота тактовый сигнал должны были быть поставлены, но мало что еще: оперативная память (RAM), контроллер RAM, поддержка шины и даже операционная система реального времени (RTOS) были встроены.

Архитектура

Оригинальный транспьютер использовал очень простую и довольно необычную архитектуру для достижения высокой производительности на небольшой площади. Он использовал микрокод в качестве основного метода управления путем к данным, но в отличие от других конструкций того времени, многие инструкции выполнялись всего за один цикл. Инструкция коды операций использовались как точки входа в микрокод только для чтения памяти (ПЗУ), а выходы из ПЗУ подавались прямо в тракт данных. Для многоцикловых инструкций, когда путь данных выполнял первый цикл, микрокод декодировал четыре возможных варианта для второго цикла. Решение о том, какой из этих вариантов будет фактически использоваться, можно будет принять ближе к концу первого цикла. Это позволило обеспечить очень быструю работу при сохранении общей архитектуры.[6]

В тактовая частота 20 МГц было довольно высоким показателем для той эпохи, и конструкторы были очень обеспокоены практичностью распределения такого быстрого тактового сигнала на плате. Использовались более медленные внешние часы 5 МГц, которые были увеличены до необходимой внутренней частоты с помощью ФАПЧ (ФАПЧ). На самом деле внутренние часы четыре неперекрывающиеся фазы и дизайнеры могли использовать любую комбинацию из них, которую они хотели, так что можно утверждать, что транспьютер действительно работал на частоте 80 МГц. Динамическая логика использовался во многих частях конструкции для уменьшения площади и увеличения скорости. К сожалению, эти методы сложно совмещать с автоматическая генерация тестовой таблицы сканирование, поэтому они перестали быть популярными для более поздних разработок.

Прентис-Холл опубликовал книгу[7] об общих принципах работы транспьютера.

Ссылки

В базовую комплектацию транспьютера входит последовательные ссылки это позволяло ему связываться с четырьмя другими транспьютерами, каждый со скоростью 5, 10 или 20 Мбит / с, что было очень быстро для 1980-х годов. Любое количество транспьютеров может быть соединено вместе по каналам (длина которых может достигать десятков метров), чтобы сформировать одно вычислительное устройство. ферма. Гипотетический настольный компьютер может иметь два «младших» транспьютера, обслуживающих ввод, вывод (I / O) задач на некоторых из их последовательных линий (подключенных к соответствующему оборудованию), пока они разговаривали с одним из своих более крупных кузенов, действующим как ЦПУ по другому.

Эта последовательная ссылка называется os-ссылкой.[8][9]

Существовали ограничения на размер системы, которую можно было построить подобным образом. Поскольку каждый транспьютер был связан с другим по фиксированной схеме «точка-точка», отправка сообщений на более удаленный транспьютер требовала, чтобы сообщения ретранслировались каждым чипом на линии. Это приводило к задержке с каждым «прыжком» по каналу, что приводило к длительным задержкам в больших сетях. Для решения этой проблемы Inmos также предоставила коммутатор с нулевой задержкой, который подключал до 32 транспьютеров (или коммутаторов) в еще более крупные сети.

Загрузка

Транспьютеры могли загружаться из памяти, как и большинство компьютеров, или по сетевым ссылкам, чтобы один транспьютер мог запустить целую сеть. Был контакт под названием BootFromROM, который при подтверждении заставлял транспьютер начинать два байта с верхней части памяти (достаточно для обратного перехода на 256 байт, обычно из ПЗУ). Когда этот вывод не был подтвержден, первый байт, пришедший по любому каналу, был длиной загружаемого файла начальной загрузки, который был помещен в низкую память и запущен. «Особые» длины 0 и 1 были зарезервированы для PEEK и POKE - разрешение проверки и замены RAM в незагруженном транспьютере. После просмотра (для чего требовался адрес) или тыка (для чего требовалось слово адрес и слово данных: 16- или 32-битное, в зависимости от базовой ширины слова варианта транспьютера) транспьютер возвращался к ожиданию бутстрап.

Планировщик

Добавлена схема расписания трафика по ссылкам. Процессы, ожидающие обмена данными, автоматически приостанавливаются, пока сетевая схема заканчивает чтение или запись. Это время будет предоставлено другим процессам, запущенным на транспьютере. В него вошли два уровни приоритета улучшить в реальном времени и мультипроцессор операция. Та же самая логическая система использовалась для связи между программами, работающими на одном транспьютере, реализованная как виртуальные сетевые ссылки в памяти. Таким образом, программы, запрашивающие любой ввод или вывод, автоматически приостанавливались на время завершения операции - задача, которая обычно требовала, чтобы операционная система выполняла роль арбитра оборудования. Операционные системы на транспьютере не нуждались в планировании; можно считать, что внутри чипа установлена ОС.

Набор инструкций

Чтобы включить все эти функции в один чип, основная логика транспьютера была проще, чем у большинства процессоров. Хотя некоторые назвали это компьютер с сокращенным набором команд (RISC) из-за его довольно разреженного характера и потому, что в то время это был желательный маркетинг модное слово, это было сильно микрокодированный, имел ограниченный набор регистров и сложные инструкции преобразования памяти в память, все из которых надежно помещали его в CISC лагерь. В отличие от регистрового загрузить / сохранить RISC ЦП, транспьютер имел только три регистра данных, которые вели себя как стек. Кроме того, указатель рабочей области указывает на обычный стек памяти, к которому легко получить доступ через инструкции. Загрузить локально и Store Local. Это позволило очень быстро переключение контекста просто изменив указатель рабочей области на память, используемую другим процессом (метод, используемый в ряде современных проектов, таких как TMS9900 ). Содержимое трех регистров стека не сохранялось после определенных инструкций, таких как Jump, когда транспьютер мог переключать контекст.

Набор команд транспьютера состоял из 8-битных инструкций, собранных из код операции и операнд грызет. В верхний nibble содержал 16 возможных кодов первичных инструкций, что делало его одним из немногих коммерчески доступных компьютеры с минимальным набором команд. В ниже nibble содержал один непосредственный постоянный операнд, обычно используемый как смещение относительно указателя рабочей области (стека памяти). Два префикс инструкции позволяли создавать более крупные константы, добавляя их младшие полубайты к операндам следующих инструкций. Дальнейшие инструкции поддерживаются с помощью кода инструкции Работать (Опр), который декодировал постоянный операнд как расширенный код операции с нулевым операндом, обеспечивая почти бесконечное и легкое расширение набора команд по мере появления новых реализаций транспьютера.

16 "первичных" однооперандных инструкций были:

| Мнемонический | Описание |

|---|---|

| J | Переход - немедленное добавление операнда к указателю инструкции |

| ЛПНП | Загрузить локальный указатель - загрузить указатель относительно рабочей области в верхнюю часть стека регистров. |

| PFIX | Префикс - общий способ увеличения младшего полубайта следующей основной инструкции |

| LDNL | Загрузить нелокально - загрузить значение смещения от адреса вверху стека |

| LDC | Загрузить константу - загрузить операнд константы в верхнюю часть стека регистров. |

| LDNLP | Загрузить нелокальный указатель - адрес загрузки, смещение от вершины стека |

| NFIX | Отрицательный префикс - общий способ отменить (и, возможно, увеличить) нижний полубайт |

| ЛПНП | Локальная загрузка - смещение значения нагрузки от рабочей области |

| АЦП | Добавить константу - добавить постоянный операнд в верхнюю часть стека регистров |

| ВЫЗОВ | Вызов подпрограммы - нажать указатель инструкции и перейти |

| CJ | Условный переход - в зависимости от значения вверху стека регистров |

| AJW | Настроить рабочее пространство - добавить операнд к указателю рабочего пространства |

| EQC | Равно константе - проверьте, равна ли верхняя часть стека регистров константе |

| STL | Хранить локально - хранить с постоянным смещением от рабочей области |

| STNL | Хранить нелокально - хранить по адресу, смещенному от вершины стека |

| OPR | Operate - общий способ расширения набора инструкций |

Все эти инструкции принимают константу, представляющую смещение или арифметическую константу. Если эта константа была меньше 16, все эти инструкции кодировались в один байт.

Первые 16 «вторичных» инструкций с нулевым операндом (с использованием первичной инструкции OPR) были:

| Мнемонический | Описание |

|---|---|

| REV | Обратный - поменять местами два верхних элемента стека регистров |

| ФУНТ | Загрузить байт |

| BSUB | Байтовый индекс |

| ENDP | Завершить процесс |

| DIFF | Разница |

| ДОБАВИТЬ | Добавлять |

| GCALL | Общий вызов - поменять местами вершину стека и указатель инструкции |

| В | Ввод - получение сообщения |

| ПРОД | Товар |

| GT | Больше чем - единственная инструкция сравнения |

| WSUB | Подстрочный индекс слова |

| ИЗ | Вывод - отправить сообщение |

| SUB | Вычесть |

| СТАРТП | Начать процесс |

| OUTBYTE | Выходной байт - отправить однобайтовое сообщение |

| СЛОВО | Выходное слово - отправить сообщение из одного слова |

Разработка

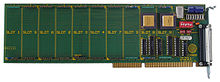

Чтобы предоставить простые средства создания прототипов, конструирования и настройки систем с несколькими транспьютерами, Inmos представила Трамвай (TRAnsputer Module) стандарт в 1987 году. ТРАМВАЙ был по сути строительным блоком дочерняя плата содержащий транспьютер и, необязательно, внешнюю память и / или периферийные устройства с простыми стандартизированными разъемами, обеспечивающими питание, транспьютерные связи, часы и системные сигналы. Были определены различные размеры ТРАМВАЙ, от базового ТРАМВА размера 1 (3,66 дюйма на 1,05 дюйма) до размера 8 (3,66 дюйма на 8,75 дюйма). Инмос произвел линейку трамваев. материнские платы для различных хост-шин, таких как Стандартная отраслевая архитектура (ЭТО), Микроканал, или же VMEbus. Линии TRAM работают со скоростью 10 Мбит / с или 20 Мбит / с.[10]

Программного обеспечения

Транспьютеры предназначались для программирования с использованием языка программирования. Оккам, на основе связь последовательных процессов (CSP) процесс исчисления. Транспьютер был построен для работы Оккам в частности, более современного CISC проекты были созданы для работы с такими языками, как Паскаль или же C. Оккам поддержал параллелизм и межпроцессное или межпроцессорное взаимодействие на основе каналов как фундаментальная часть языка. Благодаря параллелизму и коммуникациям, встроенным в чип, и языку, взаимодействующему с ним напрямую, написание кода для таких вещей, как контроллеры устройств, стало тривиальным делом; даже самый простой код может следить за последовательными портами на предмет ввода-вывода и автоматически переходить в спящий режим, когда нет данных.

Первоначальной средой разработки Оккама для транспьютера была Inmos D700. Транспьютерная система разработки (TDS). Это была необычная интегрированная среда разработки, включающая редактор, компилятор, компоновщик и (посмертный) отладчик. TDS - это транспьютерное приложение, написанное на языке Оккам. Текстовый редактор TDS отличался тем, что редактор складывания, позволяя скрывать и открывать блоки кода, чтобы сделать структуру кода более очевидной. К сожалению, сочетание незнакомого языка программирования и столь же незнакомой среды разработки никак не повлияло на раннюю популярность транспьютера. Позже Inmos выпустит более традиционные кросс-компиляторы Оккама, Наборы инструментов Occam 2.

Реализации более распространенных языков программирования, таких как C, FORTRAN, Ада и Pascal позже были выпущены как Inmos, так и сторонними поставщиками. Обычно они включали языковые расширения или библиотеки, обеспечивающие менее элегантным способом параллелизм в стиле Оккама и связь на основе каналов.

Отсутствие поддержки виртуальной памяти в транспьютере препятствовало переносу основных вариантов Unix операционная система, хотя порты Unix-подобный операционные системы (такие как Minix и Идрис из Whitesmiths ) были произведены. Продвинутый Unix-подобный распределенная операционная система, HeliOS, также был разработан специально для мульти-транспьютерных систем компанией Программное обеспечение Perihelion.

Реализации

Первые транспьютеры были объявлены в 1983 году и выпущены в 1984 году.

В соответствии с их ролью микроконтроллер Как и устройства, они включали в себя встроенную оперативную память и встроенный контроллер оперативной памяти, что позволяло добавлять больше памяти без дополнительного оборудования. В отличие от других конструкций, транспьютеры не имели линий ввода-вывода: они должны были быть добавлены с оборудованием, подключенным к существующим последовательным каналам. Была одна строка «Событие», похожая на линию прерывания обычного процессора. Рассматриваемая как канал, программа могла «входить» из канала событий и продолжать работу только после того, как была утверждена строка события.

Все транспьютеры работали от внешнего тактового входа 5 МГц; это было умножено, чтобы обеспечить тактовую частоту процессора.

Транспьютер не включал блок управления памятью (MMU) или виртуальная память система.

Варианты транспьютеров (кроме отмененного T9000) можно разделить на три группы: 16 бит Т2 серия, 32-битный Т4 серии, а 32-битный T8 серия с 64-битной IEEE 754 плавающая точка поддерживать.

T2: 16 бит

Прототип 16-битного транспьютера был S43, в котором отсутствовал планировщик и блочная передача по каналам, управляемая DMA. При запуске T212 и M212 (последний со встроенным контроллером диска) были 16-битными предложениями. T212 был доступен с тактовой частотой процессора 17,5 и 20 МГц. T212 был заменен T222, с расширением ОЗУ на кристалле с 2 КБ до 4 КБ, а позже T225. Это добавил отладку-точка останова поддержка (путем расширения инструкции "J 0") плюс некоторые дополнительные инструкции из набора команд T800. И T222, и T225 работали на частоте 20 МГц.

T4: 32-битный

При запуске T414 было 32-битным предложением. Первоначально первым 32-битным вариантом должен был стать T424, но трудности изготовления привели к тому, что он был переработан в T414 с 2 КБ встроенной оперативной памяти вместо предполагаемых 4 КБ. T414 был доступен в вариантах 15 и 20 МГц. Позднее объем оперативной памяти был восстановлен до 4 КБ. T425 (в вариантах 20, 25 и 30 МГц), который также добавил J 0 поддержка точки останова и дополнительные инструкции T800. В T400, выпущенный в сентябре 1989 года, представлял собой недорогую производную 20 МГц T425 с 2 КБ и двумя вместо четырех каналов, предназначенную для встроенные системы рынок.

T8: с плавающей точкой

Второе поколение T800 Транспьютер, представленный в 1987 году, имел расширенный набор команд. Самым важным дополнением стала 64-битная блок с плавающей запятой (FPU) и три добавленных регистра для плавающей запятой, реализующие стандарт с плавающей запятой IEEE754-1985. Он также имел 4 КБ встроенной оперативной памяти и был доступен в версиях с частотой 20 или 25 МГц. Поддержка точки останова была добавлена позже T801 и T805, первый с отдельными шинами адреса и данных для повышения производительности. Позднее T805 также был доступен с частотой 30 МГц.

Расширенный T810 планировалось, что у него было бы больше ОЗУ, больше и более быстрых ссылок, дополнительных инструкций и улучшенного микрокода, но это было отменено примерно в 1990 году.

Компания Inmos также произвела различные микросхемы поддержки для процессоров транспьютеров, такие как C004 32-позиционный переключатель связи и C011 и C012 «адаптеры связи», которые позволяли подключать транспьютерные каналы к 8-битной шине данных.

T400

Частью первоначальной стратегии Inmos было сделать процессоры настолько маленькими и дешевыми, чтобы их можно было объединить с другой логикой в одном устройстве. Хотя система на чипе (SoC), как их обычно называют, сейчас повсеместно распространены, концепция была почти неслыханной еще в начале 1980-х годов. Примерно в 1983 году были начаты два проекта: M212 и ТВ-игрушка. M212 был основан на стандартном ядре T212 с добавлением контроллера диска для стандартов ST 506 и ST 412 Shugart. ТВ-игрушка должна была стать основой для игровая приставка и был совместным проектом Inmos и Sinclair Research.

Связи в транспютерах T212 и T414 / T424 имели аппаратные механизмы DMA, так что передачи могли происходить параллельно с выполнением других процессов. Был разработан вариант конструкции, получивший название T400, не путать с более поздним транспьютером с таким же названием, в котором ЦП обрабатывал эти передачи. Это значительно уменьшило размер устройства, поскольку 4-канальные механизмы были примерно такого же размера, как и весь ЦП. T400 предназначался для использования в качестве ядра в том, что тогда называлось системы на кремнии (SOS) устройства, теперь называемые и более известные как система на чипе (SoC). Именно эта конструкция должна была стать частью ТВ-игрушки. Проект был закрыт в 1985 году.

T100

Хотя предыдущие проекты SoC имели лишь ограниченный успех (M212 продавался какое-то время), многие дизайнеры все еще твердо верили в эту концепцию, и в 1987 году был запущен новый проект T100, который объединил 8-битную версию транспьютера. ЦП с настраиваемой логикой на основе конечных автоматов. Набор команд транспьютера основан на 8-битных инструкциях и может легко использоваться с любым размером слова, кратным 8 битам. Целевым рынком для T100 должны были стать контроллеры шины, такие как Futurebus, а также обновление для стандартных адаптеров связи (C011 и т. Д.). Проект был остановлен, когда был запущен T840 (впоследствии ставший основой T9000).

- Транспьютеры серий T2, T4 и T8

Inmos T212, ПРЕДВАРИТЕЛЬНЫЙ

Inmos T222, ПРЕДВАРИТЕЛЬНЫЙ

STMicroelectronics IMST225 (Inmos T225)

Inmos T400

Inmos T414

Inmos T425

Inmos T800, ПРЕДВАРИТЕЛЬНЫЙ

STMicroelectronics IMST805 (Inmos T805)

TPCORE

TPCORE - это реализация транспьютера, включая os-link, который работает в FPGA.[8][11]

T9000

Inmos улучшила производительность транспьютеров серии T8 с введением T9000 (под кодовым названием H1 во время разработки). T9000 разделял большинство функций с T800, но переместил некоторые элементы дизайна в оборудование и добавил несколько функций для суперскалярный поддерживать. В отличие от более ранних моделей, T9000 имел настоящую высокоскоростную память 16 КБ. тайник (с использованием случайной замены) вместо ОЗУ, но также позволял использовать ее в качестве памяти и включал функциональность, подобную MMU, для обработки всего этого (так называемая PMI). Для большей скорости T9000 кэширует 32 верхних местоположения стека вместо трех, как в более ранних версиях.

T9000 использовал пятиступенчатый конвейер для еще большей скорости. Интересным дополнением стал морской окунь[12] который будет собирать инструкции из кеша и группировать их в более крупные пакеты до 8 байтов, чтобы ускорить загрузку конвейера. Затем группы завершались за один цикл, как если бы они были отдельными большими инструкциями, работающими на более быстром процессоре.

Система каналов была модернизирована до нового режима 100 МГц, но, в отличие от предыдущих систем, каналы связи больше не были совместимы вниз. Этот новый протокол пакетной связи был назван DS-Link,[13] а позже легли в основу IEEE 1355 стандарт последовательного межсоединения. В T9000 также добавлено оборудование для маршрутизации каналов, называемое VCP (Процессор виртуального канала), который изменил связи от точки к точке на настоящую сеть, позволяя создавать любое количество виртуальные каналы по ссылкам. Это означало, что программам больше не нужно было знать физическую схему соединений. Также был разработан ряд микросхем поддержки DS-Link, включая C104 32-позиционный переключатель перекладины и C101 адаптер связи.

Длительные задержки в разработке T9000 означали, что более быстрые конструкции загрузки / сохранения уже превосходили его по производительности к тому моменту, когда он должен был быть выпущен. Ему постоянно не удавалось достичь своей цели по производительности - превзойти T800 в десять раз. Когда проект был окончательно отменен, он все еще достигал лишь около 36 MIPS на частоте 50 МГц. Задержки в производстве вызвали шутку о том, что лучшей хост-архитектурой для T9000 был оверхед.

Это было слишком много для Inmos, у которой не было финансирования, необходимого для продолжения разработки. К этому времени компания была продана SGS-Thomson (сейчас STMicroelectronics ), в центре внимания которого был рынок встраиваемых систем, и в конечном итоге от проекта T9000 отказались. Однако полностью переработанный 32-битный транспьютер, предназначенный для встраиваемых приложений, ST20 серия, позже была произведена с использованием некоторых технологий, разработанных для T9000. Ядро ST20 было включено в чипсеты для телеприставки и спутниковая система навигации (GPS) приложения.

ST20

Хотя это не совсем транспьютер, ST20 находился под сильным влиянием T4 и T9 и лег в основу T450, который, возможно, был последним из транспьютеров. Миссия ST20 заключалась в том, чтобы стать многоразовым ядром на развивающемся тогда рынке SoC. Первоначальное название ST20 было многоразовым микроядром (RMC). Архитектура была основана на исходной архитектуре T4 с каналом данных, управляемым микрокодом. Однако это был полный редизайн с использованием VHDL как язык проектирования и с оптимизированным (и переписанным) компилятором микрокода. Проект был задуман еще в 1990 году, когда стало ясно, что T9 будет слишком большим для многих приложений. Фактические проектные работы начались в середине 1992 года. Было выполнено несколько пробных проектов, от очень простого ЦП в стиле RISC со сложными инструкциями, реализованными в программном обеспечении с помощью ловушек, до довольно сложной суперскалярной конструкции, аналогичной концепции Алгоритм Томасуло. Окончательный дизайн выглядел очень похожим на исходное ядро T4, хотя некоторые простые группы инструкций и кеш рабочей области были добавлены для повышения производительности.

Принятие

Хотя транспьютер был простым, но мощным по сравнению со многими современными конструкциями, он так и не приблизился к достижению своей цели - универсального использования как в процессоре, так и в микроконтроллере. На рынке микроконтроллеров доминировали 8-битные машины, где стоимость была самым важным фактором. Здесь даже T2 были слишком мощными и дорогими для большинства пользователей.

в рабочий стол компьютера и рабочая станция месторождении транспьютер был довольно быстрым (работала около 10 миллионов инструкций в секунду (MIPS) на 20 МГц). Это был отличный результат для начала 1980-х, но к тому времени блок с плавающей запятой (FPU) T800 был отгружен, другие конструкции RISC превзошли его. Это можно было бы в значительной степени смягчить, если бы машины использовали несколько транспьютеров, как и планировалось, но T800 стоили около 400 долларов каждый, что означало плохое соотношение цены и производительности. Было разработано несколько систем рабочих станций на базе транспьютеров; наиболее примечательным, вероятно, является Рабочая станция Atari Transputer.

Транспьютер оказался более успешным в области массивно параллельный computing, где в конце 1980-х годов несколько поставщиков производили системы на базе компьютеров. К ним относятся Meiko Scientific (основан бывшими сотрудниками Inmos), Системы с плавающей запятой, Парсайтек,[14] и парсы. Несколько британских академических институтов начали исследовательскую деятельность по применению транспьютерных параллельных систем, в том числе Бристольский политехнический институт Бристольский транспортный центр и Эдинбургский университет с Эдинбургский суперкомпьютер параллельной работы Проект. Кроме того, системы сбора данных и запуска второго уровня физики высоких энергий. ЗЕВС Эксперимент для Адронное электронное кольцо Anlage (HERA) коллайдер на DESY был основан на сети из более чем 300 синхронно синхронизируемых транспьютеров, разделенных на несколько подсистем. Они управляли как считыванием пользовательской электроники детектора, так и запускали алгоритмы реконструкции для выбора физических событий.

Возможности параллельной обработки транспьютера были коммерчески использованы для обработка изображений крупнейшей в мире полиграфической компанией, Р. Р. Доннелли и сыновья, в начале 1990-х гг. Возможность быстро преобразовывать цифровые изображения при подготовке к печати дала компании значительное преимущество перед конкурентами. Этой разработкой руководил Майкл Бенгтсон из технологического центра RR Donnelley. В течение нескольких лет возможности обработки даже настольных компьютеров отпали необходимость в специализированных многопроцессорных системах для компании.[нужна цитата ]

Немецкая компания Jäger Messtechnik использовала транспьютеры в своей ранней версии ADwin, работающей в реальном времени. получение данных и контрольные продукты.[15]

Транспьютеры также нашли применение в анализаторах протоколов, таких как Siemens / Tektronix K1103, и в военных приложениях, где архитектура массива подходила для таких приложений, как радар, и последовательные каналы (которые были высокоскоростными в 1980-х годах) хорошо служили для экономии затрат и веса в суб- системные коммуникации.

Транспьютер также появился в продуктах, связанных с виртуальная реальность например, система ProVision 100, производимая компанией Division Limited из Бристоля, с комбинацией Intel i860, 80486 / 33 и Toshiba Процессоры HSP вместе с транспютерами T805 или T425, реализующие движок рендеринга который затем может быть доступен как сервер к ПК, Солнечная SPARCstation или же VAX системы.[16][17]

Мириада, европейский миниатюрный спутник платформа, разработанная Спутники Astrium и CNES и используется такими спутниками, как Пикард, основан на T805 с производительностью около 4 MIPS и планируется оставить в производстве примерно до 2015 года.[18][19]

Асинхронная операция связи и вычислений позволила разработать асинхронные алгоритмы, такие как алгоритм Бэйна «Асинхронный полиномиальный поиск нуля».[20] Область асинхронных алгоритмов и асинхронная реализация текущих алгоритмов, вероятно, сыграет ключевую роль в переходе к эксафлопсные вычисления.

В Исследователь переходных процессов высоких энергий 2 (HETE-2) использовали 4 транспютера T805 и 8 DSP56001, что дало около 100 миллионов инструкций в секунду (MIPS) производительности.[21]

Наследие

Эта секция написано как личное размышление, личное эссе или аргументированное эссе который излагает личные чувства редактора Википедии или представляет оригинальный аргумент по теме. (Февраль 2019 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

Растущий внутренний параллелизм стал одной из движущих сил улучшений в традиционных конструкциях ЦП. Вместо явного параллелизма на уровне потоков (который используется в транспьютере) конструкции ЦП использовали неявный параллелизм на уровне инструкций, проверяя последовательности кода на зависимости данных и выдавая несколько независимых инструкций различным исполнительным блокам. Это называется суперскалярный обработка. Суперскалярные процессоры подходят для оптимизации выполнения последовательно построенных фрагментов кода. Сочетание суперскалярной обработки и спекулятивное исполнение обеспечил ощутимое повышение производительности существующих фрагментов кода, которые в основном были написаны на Паскале, Фортране, C и C ++. Учитывая эти существенные и регулярные улучшения производительности существующего кода, не было большого стимула переписывать программное обеспечение на языках или стилях кодирования, которые открывают больший параллелизм на уровне задач.

Тем не менее, модель взаимодействующих параллельных процессоров все еще можно найти в кластерные вычисления системы, которые доминируют суперкомпьютер дизайн в 21 веке. В отличие от транспьютерной архитектуры, в процессорах этих систем обычно используются суперскалярные процессоры с доступом к значительным объемам памяти и дискового хранилища, работающие под управлением обычных операционных систем и сетевых интерфейсов. Из-за более сложных узлов программная архитектура, используемая для координации параллелизма в таких системах, обычно намного тяжелее, чем в транспьютерной архитектуре.

Фундаментальный мотив транспьютеров остается, но более 20 лет маскировался повторным удвоением количества транзисторов. Неизбежно, что у разработчиков микропроцессоров, наконец, закончилось использование больших физических ресурсов, почти в то же самое время, когда масштабирование технологий начало достигать своих пределов. Потребляемая мощность и, следовательно, потребности в тепловыделении, обеспечивают дальнейшее тактовая частота увеличение неосуществимо. Эти факторы привели отрасль к решениям, мало отличающимся по сути от решений, предлагаемых Inmos.

Самые мощные суперкомпьютеры в мире, созданные на основе разработок Колумбийский университет и построен как IBM Синий ген, являются реальным воплощением транспьютерной мечты. Это огромные сборки идентичных, относительно низкопроизводительных SoC.

Последние тенденции также пытались решить дилемму транзисторов способами, которые были бы слишком футуристичными даже для Inmos. Помимо добавления компонентов в кристалл ЦП и размещения нескольких кристаллов в одной системе, современные процессоры все чаще размещают несколько ядер на одном кристалле. Разработчики транспьютеров изо всех сил пытались уместить хотя бы одно ядро в свой транзисторный бюджет. Сегодня конструкторы, работающие с увеличением плотности транзисторов в 1000 раз, обычно могут разместить много. Одна из самых последних коммерческих разработок фирмы XMOS, которая разработала семейство встраиваемых многоядерных многопоточных процессоров, которые хорошо работают с транспьютером и Inmos. Появляется новый класс многоядерных / многоядерных процессоров, использующих подход сеть на чипе (NoC), например Сотовый процессор, Адаптева Богоявленская архитектура, Тилера и др.

Транспьютер и Inmos помогли установить Бристоль, Великобритания, как центр разработки и инноваций в области микроэлектроники.

Смотрите также

- Адаптева

- Дэвид Мэй (ученый-компьютерщик)

- Легкость (язык программирования)

- IEEE 1355

- Inmos

- iWarp

- Вычислительная поверхность Meiko

Рекомендации

- ^ Аллен Кент, Джеймс Г. Уильямс (ред.) (1998) «Энциклопедия компьютерных наук и технологий», ISBN 0-8247-2292-2, «Семейство продуктов Transputer», Хамид Р. Арабния.

- ^ Привет, Энтони Дж. Г. (01.01.1990). «Суперкомпьютеры с Transputers - прошлое, настоящее и будущее». Материалы 4-й Международной конференции по суперкомпьютерам.. ICS '90. Нью-Йорк, Нью-Йорк, США: ACM: 479–489. Дои:10.1145/77726.255192. ISBN 0897913698. S2CID 8612995.

- ^ Фуллер, Сэмюэл Х. и Миллетт, Линетт И., редакторы (2011). Будущее вычислительной производительности, CSTB, Национальная академическая пресса, стр. 84. ISBN 978-0-309-15951-7 Проверено 2 ноября, 2016.

- ^ "Премия принца Филиппа дизайнеров". The Design Council. Получено 2019-12-01.

- ^ Barron, Iann M. (1978). D. Aspinall (ed.). "The Transputer". The Microprocessor and Its Application: An Advanced Course. Издательство Кембриджского университета: 343. ISBN 0-521-22241-9. Получено 2009-05-18.

- ^ Stakem, Patrick H. The Hardware and Software Architecture of the Transputer, 2011, PRB Publishing, ASIN B004OYTS1K

- ^ Transputer Reference Manual (PDF). Prentice-Hall. 1988. ISBN 0-13-929001-X.

- ^ а б Kazuto Tanaka; Satoshi Iwanami; Takeshi Yamakawa; Chikara Fukunaga; Kazuto Matsui; Takashi Yoshida."The Design and Performance of SpaceWire Router-network using CSP".p. 2.

- ^ "High-Performance Computing and Networking: International Conference and Exhibition, Amsterdam, The Netherlands, April 21-23, 1998 Proceedings".B C O'Neill; G Coulson; K L Wong; R Hotchkiss; J H Ng; S Clark; and P D Thomas."An Interface Device to Support a Distributed Parallel System for the StrongARM Microprocessor".p. 1031.

- ^ "Inmos Technical Note 29: Dual-In-Line Transputer Modules (TRAMs)". Transputer.net. 2008-07-04. Получено 2013-10-12.

- ^ "Communicating Process Architectures 2004".p. 361.Makoto Tanaka; Naoya Fukuchi; Yutaka Ooki; and Chikara Fukunaga."Design of a Transputer Core and its implementation in an FPGA".2004.

- ^ Inmos T9000 CPU patent, "US patent 5742783",

- ^ Inmos DS Link patent, "Communication Interface US patent 5341371"

- ^ Harald W. Wabnig (20–22 September 1993). Virtual Channels for Deadlock-Free Communication in Transputer Networks. 1993 World Transputer Congress. Aachen, Germany. п. 1047. ISBN 9789051991406.

- ^ "ADwin Fast Real-Time Automation System" (PDF). Архивировано из оригинал (PDF) на 2012-04-25. Получено 2011-11-16.

- ^ Edmunds, Nick (July 1993). "When two worlds collide". Personal Computer World.

- ^ Bangay, Sean (July 1993). Parallel Implementation of a Virtual Reality System on a Transputer Architecture (PDF). Родосский университет. Получено 2012-05-06.

- ^ "The Myriade Platform". Получено 2011-08-22.

- ^ David Chemouil. "The Design of Space Systems" (PDF). Архивировано из оригинал (PDF) на 2012-03-21. Получено 2011-08-22.

- ^ T.L. Freeman and M.K. Bane, "Asynchronous Polynomial Zero-Finding Algorithms". Parallel Computing 17, pp. 673-681. (1991)

- ^ HETE-2 Spacecraft

внешняя ссылка

- The Transputer FAQ

- Ram Meenakshisundaram's Transputer Home Page

- WoTUG A group applying the principles of transputers (e.g., communicating sequential processes (CSP)) in other environments.

- Transputer emulator – It emulates one T414 transputer (i.e., no FPU, no blitting instructions) and supplies the file and terminal I/O services that were usually supplied by a host computer system.

- PC-based Transputer emulator – This is a PC port of the original T414 transputer emulator (called jserver) written by Julian Highfield in the mid- to late 1990s.

- Transputers can be fun.

- The Transterpreter virtual machine. – A portable runtime for occam-pi and other languages based on the transputer bytecode.

- The Kent Retargettable occam compiler. – The occam-pi compiler.

- transputer.net. – Documents and more about transputer.

- Inmos alumni Directory of ex-Inmos employees, plus photos and general info. Maintained by Ken Heddings.

- Prince Philip Designers Prize winners from 1959 to 2009, Design Council website

- HETE-2 Spacecraft internal systems