Signetics 8X300 - Signetics 8X300

В 8X300 это микропроцессор производится и продается Печатки начиная с 1976 г. в качестве второго источника SMS 300 компании Scientific Micro Systems, Inc.[1][2][3][4]

Хотя SMS разработала продукты SMS 300 / 8X300, Signetics была единственным производителем этой линейки продуктов. В 1978 году Signetics приобрела права на серию SMS300 и переименовала SMS300 в 8X300.

Он был разработан, чтобы быть быстрым микроконтроллер и сигнальный процессор, и из-за этого значительно отличается от обычных Логика NMOS микропроцессоры того времени. Возможно, основным отличием было то, что он был реализован с биполярным Транзистор шоттки Технология и может извлекать, декодировать и выполнять команду всего за 250 нс. Данные могут быть введены с одного устройства, изменены и выведены на другое устройство в течение одного цикла команд.

В 1982 году Signetics выпустила улучшенную и более быструю версию 8X305. Этот процессор стал очень популярным в военных приложениях и был второй источник к Продвинутые Микроустройства как AM29X305. В конце концов, права на производство были проданы Lansdale Semiconductor Inc., которая по состоянию на 2017 год все еще предлагала 8X305.[5] Клон 8X300 был произведен в Советский союз под обозначение KM1818VM01 (русский: КМ1818ВМ01).[4]

Архитектура

Устройство поставлялось в керамическом корпусе DIL с 50 выводами и питалось от одной шины питания 5 В. Транзистор с внешним проходом требовался для завершения встроенного регулятора напряжения, который подавал 3 В на выбранные участки микросхемы. Это помогло поддерживать общий ток, потребляемый микросхемой, менее 450 мА.

Требования к тактовой частоте были выполнены путем подключения кристалла 8 МГц напрямую к двум контактам. В качестве альтернативы можно использовать противофазные сигналы от внешнего тактового генератора.

Вторая уникальная особенность - это выделенный 13-битный адрес и 16-битная шина данных для доступа к программной памяти, что позволяет напрямую адресовать 8192 16-битных программных слов. Это позволяло напрямую подключать программную память ROM / PROM без дополнительного оборудования. Вторая комбинированная 8-битная шина адреса / данных - шина вектора интерфейса (IV) использовалась для данных и ввода / вывода. Два управляющих сигнала - WC (команда записи) и SC (команда выбора) определяют состояние шины IV следующим образом:

- SC = 1, WC = 0 Адрес ввода / вывода выводится на шину IV

- SC = 0, WC = 1 Данные ввода / вывода выводятся на шину IV

- SC = 0, WC = 0 Входные данные ввода / вывода ожидаются на шине IV

Еще два сигнала; LB (выбор левого банка) и RB (выбор правого банка) эффективно удваивали адресное пространство шины IV и чаще всего использовались для переключения между памятью RAM в одном банке и портами ввода-вывода в другом.

Еще одна необычная особенность заключалась в том, что вместо выполнения масок инструкции поворота, сдвига и слияния в арифметико-логическое устройство (ALU), как и в случае с большинством микропроцессоров, 8X300 имел отдельные блоки маски, поворота, сдвига и слияния. Таким образом, данные можно было вращать, маскировать, изменять, сдвигать и объединять (в указанном порядке) за один цикл команд.

Набор инструкций

Процессор обычно обрабатывает 8-битные байты данных, но блок маски позволяет манипулировать одним или несколькими битами, что делает его процессором переменной длины. Внутренние данные хранятся в 8-битных регистрах чтения / записи - с R1 по R6, R9 и во вспомогательном регистре (R0). Вспомогательный регистр содержит один из операндов, используемых в двухоперандных инструкциях, таких как ADD или AND, а однобитовый (только для чтения) регистр переполнения (R8) хранит бит переноса из операций добавления. Два виртуальных писать только регистры IVL (R7) и IVR (R15) используются для размещения адреса на шине IV, а два набора из восьми виртуальных регистров (R16-R23 и R24-R31) используются для передачи данных на шину IV или с нее. В последнем случае два верхних бита номера регистра выбирают левый или правый банк, а три нижних бита определяют количество мест, в которых данные должны быть повернуты. 8-битный буфер IV-шины сохраняет копию последние данные, передаваемые на шину IV или с нее. Эти данные используются в операциях слияния.

Три наиболее значимых бита инструкции определяют код операции, и разделите инструкции на 8 классов:

- Команда MOVE позволяет скопировать содержимое выбранных регистров, поместить на шину IV или наоборот.

- Классы ADD, AND и XOR аналогичны, за исключением того, что в этих инструкциях содержимое вспомогательного регистра объединяется с исходным регистром перед выполнением части инструкции MOVE.

- Команда XEC позволяет выполнить выбранную команду по другому адресу без увеличения счетчика программы.

- Инструкция NZT позволяет реализовать условный переход.

- Команда XMIT позволяет разместить 8-битный двоичный шаблон, указанный в инструкции, в указанном регистре или на шине IV. Это похоже на инструкцию немедленной загрузки.

- Инструкция JMP выполняет безусловный переход в любую точку памяти программы на 8192 слов.

Использование оставшихся 13 бит инструкции зависит от кода операции:

- Инструкции MOVE, AND, ADD и XOR: 5 битов используются для определения исходного регистра, 3 бита используются для определения любой операции поворота или маскирования (поле R / L), а оставшиеся 5 битов определяют регистр назначения.

- XEC и NZT: 5 битов используются для определения исходного регистра, остальные 8 битов определяют поле адреса.

- XEC: содержимое исходного регистра сначала добавляется в поле адреса, которое затем используется как младшие 8 бит адреса программы.

- NZT: переход выполняется, если исходный регистр не равен нулю. Если выполняется переход, поле адреса используется как младшие 8 бит адреса программы.

- XMIT: 5 бит используются для определения регистра назначения, остальные 8 бит определяют данные.

- JMP: все 13 битов используются как абсолютный адрес в программной памяти.

Сдвиг, поворот, маска и слияние

Блоки поворота и маски расположены между банком регистров и ALU. Следовательно, все данные, в принципе, могут быть повернуты и замаскированы до того, как они попадут в ALU.

- Повернуть блок: этот блок поворачивает данные ВПРАВО на количество разрядов, указанное в коде операции.

- Единица маски: эта единица маскирует (устанавливает в ноль) верхние биты данных, чтобы сохранить количество младших битов, указанных в коде операции.

Блоки сдвига и слияния расположены между ALU и шиной IV, поэтому любые данные, отправленные на шину IV, могут быть сдвинуты и объединены перед выводом.

- Блок сдвига: этот блок сдвигает данные ВЛЕВО на количество мест, указанное в коде операции.

- Блок слияния: этот блок объединит (заменит) количество битов, заданное кодом операции в буфере IV-шины, с данными с перед размещением содержимого буфера на IV-шине.

Примечание: нулевой счетчик количества битов для слияния приведет к замене всех 8 бит.

В зависимости от источника и назначения возможны следующие комбинации:

- Инструкции MOVE, ADD, AND и XOR:

- регистр для регистрации (включая регистры IVL и IVR): повернуть

- регистр на IV-шину (вывод данных): сдвиг и объединение

- Вход IV-шины для регистрации: поворот и маска

- Вход IV-bus на выход IV-bus: поворот, маска, сдвиг и объединение

- Вход IV-шины в регистр IVL или IVR (выход адреса IV-шины): поворот и маска

- XEC и NZT:

- Вход шины IV: поворот и маска

- XMIT

- IV-шина (вывод данных): сдвиг и слияние

Ввод / вывод

Передача данных на 8X300 и обратно - это двухэтапный процесс:

- 1 Используя одну из инструкций MOVE, ADD, AND, XOR или XMT и указав один из виртуальных регистров IVL (левый банк) или IVR (правый банк) в качестве назначения, адрес выводится на шине IV вместе с командой выбора и сигналы выбора банка.

Поскольку адрес ввода / вывода выводится отдельно, порты ввода / вывода должны удерживать (фиксировать) выбор. Это можно сделать с помощью отдельных декодеров адресов и защелок или с помощью порта ввода-вывода со встроенным декодированием и фиксацией адреса, такого как 8X32. Из-за фиксации порты ввода-вывода после адресации остаются активными до тех пор, пока не будет установлен другой адрес. выводятся, и к ним можно обращаться несколько раз без необходимости повторять их. Два порта ввода-вывода (или адреса ОЗУ) могут быть активными одновременно, с помощью сигналов выбора банка для быстрого переключения между ними без дальнейшей адресации.

- 2 Данные передаются в 8X300 или из него с использованием одной из инструкций MOVE, ADD, AND или XOR и указания одного из регистров R16-R31 в качестве источника и / или назначения. Выбранный регистр определяет, какой сигнал выбора банка сопровождает перевод.

Приложения

В обширной заметке по применению Signetics показала, как использовать 8X300 в качестве контроллер гибких дисков В пересмотренном примечании по применению показано использование 8X300 вместе с 8X330. Описание других примечаний по применению:

- А телетайп мультиплексор

- Концентратор данных

- Контроллер удаленного терминала

- Эмулятор компьютерной шины ввода-вывода

- Интерфейс оперативной памяти

Демонстрационная система (находится в портфеле) и инструкция по применению показали, что 8X300 используется в контроллере светофора.

Olivetti использовал 8X300 и более поздние модели 8X305 в качестве контроллера для жесткого диска ST506 в M20 серия персональных компьютеров.

Конвергентные технологии использовали 8X300I в своем контроллере жестких дисков AWS в 1981 году.

Устройства поддержки

- 8X01 Циклический контроль избыточности

- 8X31 / 8T31 8-битный двунаправленный порт ввода-вывода с защелкой

- 8X32 / 8X36 / 8X42 8-битный адресный двунаправленный порт ввода-вывода с защелкой

- 8T39 Расширитель адресной шины

- 8X41 Асинхронный двунаправленный расширитель и повторитель шины (SABRE)

- 8T58 Прозрачный расширитель шины

- Массив регистров интерфейса шины 8X320

- Контроллер / форматер гибких дисков 8X330

- 8X350 2048-битное биполярное ОЗУ (256 * 8), время доступа 35 нс

- SMS360 / 8X360 Интерфейсный векторный байт

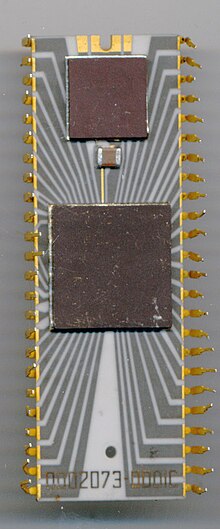

- Chip and die фото

Signetics N8X300I - начало 1978 г.

Signetics N8X300I - 1981 г.

Умереть Signetics 8X300

Умереть Signetics 8X305

Рекомендации

- ^ Руководство по проектированию 8X300, Signetics Corporation, ноябрь 1980 г., документ DSPG 80-102

- ^ Быстрый 8-битный биполярный микропроцессор, Дэвид Эдвардс, ELECTRONICS Australia, март 1978 г.

- ^ Signetics / SMS 300 Pact, Microcomputer Digest vol. 2, No. 11, май 1976 г.

- ^ а б «История процессоров SMS300 и Signetics 8X300». CPUShack. 16 ноября 2010 г.. Получено 5 января 2017.

- ^ «Микроконтроллер SL8X305» (PDF). Lansdale Semiconductor Inc.. Получено 20 июн 2017.