Intel 8255 - Intel 8255

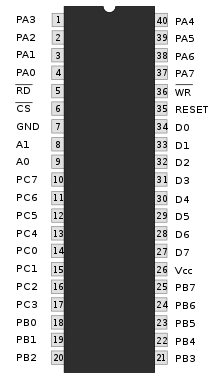

В Intel 8255 (или же i8255) Программируемый Периферийный Интерфейс (PPI) был разработан и изготовлен Intel в первой половине 1970-х годов для Intel 8080 микропроцессор. 8255 имеет 24 параллельных входных / выходных линии с различными программируемыми режимами работы.

8255 является членом Семейство MCS-85 микросхем, разработанных Intel для использования с их 8085 и 8086 микропроцессоры и их потомки.[1] Впервые он был доступен в 40-контактном ОКУНАТЬ а позже 44-контактный PLCC пакеты.[2] Он нашел широкое применение в системах цифровой обработки и позже был клонирован другими производителями. 82C55 - это CMOS версия для более высокой скорости и меньшего потребления тока.

Функциональность 8255 теперь в основном встроена в более крупные СБИС обработка чипов как подфункция. А CMOS версия 8255 все еще производится[3] к Renesas но в основном используется для расширения ввода / вывода микроконтроллеры.

Подобные фишки

8255 имеет функции, аналогичные Технология MOS 6522 (Универсальный интерфейсный адаптер) и 6526 MOS Technology ЦРУ (Комплексный интерфейсный адаптер), оба разработаны для 6502 семья.

Все эти микросхемы изначально были доступны в DIL-корпусе с 40 выводами. 8255 имеет 24 используемых контакта ввода / вывода, тогда как микросхемы MOS имеют только 16 контактов ввода / вывода плюс 4 контакта управления. Однако микросхемы MOS содержат больше функций, таких как два программируемых таймера перезагрузки и простая функция регистра сдвига ввода / вывода. Кроме того, устройства MOS позволяют индивидуально программировать направление (вход или выход) всех их выводов ввода / вывода. Контакты ввода / вывода 8255 имеют только четыре программируемых бита направления: один для всего порта A (7: 0), один для порта B (7: 0), один для порта C (3: 0) и один для порта C ( 7: 4).

Другими сопоставимыми микросхемами ввода-вывода микропроцессора являются программируемый периферийный интерфейс 2655 от Печатка 2650 семья, Motorola 6820 PIA (Адаптер периферийного интерфейса) из Motorola 6800 семья и Центр западного дизайна WDC 65C21.

Варианты

Версия Intel ID8255A промышленного уровня была доступна по цене 17,55 долларов США при количестве от 100 штук и выше.[4] Доступная версия Intel 8255A-5 стоила 6,55 долларов США при количестве 100 или более.[5]

Приложения

8255 широко использовался во многих системах микрокомпьютеров / микроконтроллеров и домашние компьютеры такой как SV-328 и все MSX модели. Модель 8255 использовалась в оригинальном IBM-PC,[6] PC / XT, PC / jr и клоны, а также многочисленные домашние компьютеры такой как N8VEM.

Функция

8255 предоставляет ЦП или цифровой системе доступ к программируемой параллельной Ввод / вывод.[7]8255 имеет 24 входа / выхода.[8] Они разделены на три 8-битных порта (A, B, C).[9] Порт A и порт B могут использоваться как 8-битные порты ввода / вывода. Порт C может использоваться как 8-битный порт ввода / вывода или как два 4-битных порта ввода / вывода или для выработки сигналов подтверждения для портов A и B.

Три порта далее сгруппированы следующим образом:

- Группа A, состоящая из порта A и верхней части порта C.

- Группа B, состоящая из порта B и нижней части порта C.

Доступны восемь линий данных (D0 – D7) (с 8-битным буфером данных) для чтения / записи данных в порты или управляющий регистр под статусом RD (вывод 5) и WR (вывод 36), которые являются сигналами активного низкого уровня для операций чтения и записи соответственно. Адресные строки A1 и А0 разрешить доступ к регистру данных для каждого порта или контрольному регистру, как указано ниже:

А1 А0 Порт выбран 0 0 порт А 0 1 порт B 1 0 порт C 1 1 контрольный регистр

Выбор чипа сигнала управления CS (вывод 6) используется для включения микросхемы 8255. Это сигнал активного низкого уровня, т.е. когда CS = 0, 8255 включен. В ПЕРЕЗАГРУЗИТЬ вход (контакт 35) подключен к линии сброса системы, например 8085, 8086 и т. д., так что при сбросе системы все порты инициализируются как входные линии. Это сделано для предотвращения разрушения 8255 и / или любого подключенного к нему периферийного устройства из-за несоответствия портов. В качестве примера рассмотрим устройство ввода, подключенное к 8255 через порт A. Если после предыдущей операции порт A инициализирован как порт вывода, и если 8255 не был сброшен до использования текущей конфигурации, то существует вероятность повреждения любого из них. подключенное устройство ввода или 8255, или оба, так как и 8255, и подключенное устройство будут отправлять данные.

Регистр управления (или логика управления, или регистр командного слова) - это 8-битный регистр, используемый для выбора режимов работы и обозначения ввода / вывода портов.[10]

Режимы работы 8255

8255 имеет два основных режима работы:

- Режим установки / сброса битов (режим BSR).

- Режим ввода / вывода (режим ввода / вывода).

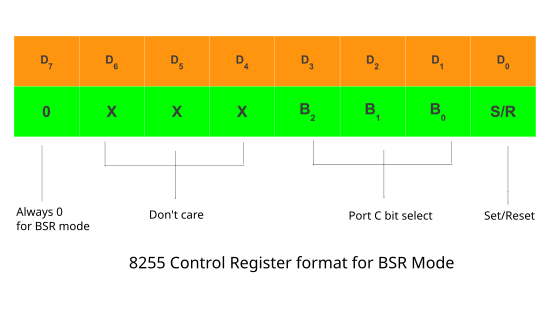

Два режима выбираются на основе значения, представленного на D7 бит регистра управляющего слова. Когда D7 = 1, 8255 работает в режиме ввода-вывода, а когда D7 = 0, работает в режиме BSR.

Режим установки / сброса битов (BSR)

Режим установки / сброса битов (BSR) доступен только для порта C. Каждая линия порта C (ПК7 - ПК0) можно установить или сбросить, записав подходящее значение в регистр управляющего слова. Режим BSR и режим ввода-вывода независимы, и выбор режима BSR не влияет на работу других портов в режиме ввода-вывода.[11]

- D7 бит всегда равен 0 для режима BSR.

- Биты D6, D5 и D4 это все равно биты.

- Биты D3, D2 и D1 используются для выбора контакта порта C.

- Бит D0 используется для установки / сброса выбранного контакта порта C.

Выбор вывода порта C определяется следующим образом:

| D3 | D2 | D1 | Выбран бит / вывод порта C |

|---|---|---|---|

| 0 | 0 | 0 | ПК0 |

| 0 | 0 | 1 | ПК1 |

| 0 | 1 | 0 | ПК2 |

| 0 | 1 | 1 | ПК3 |

| 1 | 0 | 0 | ПК4 |

| 1 | 0 | 1 | ПК5 |

| 1 | 1 | 0 | ПК6 |

| 1 | 1 | 1 | ПК7 |

Например, если необходимо, чтобы ПК5 быть установлен, то в контрольном слове,

- Поскольку это режим BSR, D7 = '0'.

- Поскольку D4, D5, D6 не используются, предположим, что они0'.

- ПК5 должен быть выбран, следовательно, D3 = '1', D2 = '0', D1 = '1'.

- ПК5 должен быть установлен, следовательно, D0 = '1'.

Таким образом, согласно приведенным выше значениям, 0B (шестнадцатеричный) будет загружен в регистр управляющего слова (CWR).

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

Режим ввода / вывода

Этот режим выбирается, когда D7 бит регистра управляющего слова равен 1. Существует три режима ввода-вывода:[12]

- Режим 0 - простой ввод / вывод

- Режим 1 - Стробированный ввод / вывод

- Режим 2 - Стробированный двунаправленный ввод / вывод

Формат контрольного слова

- D0, D1, D3, D4 назначены для порта C нижнего, порта B, порта C верхнего и порта A соответственно. Когда эти биты 1, соответствующий порт действует как входной порт. Например, если D0 = D4 = 1, то нижний порт C и порт A действуют как входные порты. Если эти биты 0, то соответствующий порт действует как выходной порт. Например, если D1 = D3 = 0, тогда порт B и верхний порт C действуют как выходные порты.

- D2 используется для выбора режима группы B (порт B и нижний порт C). Когда D2 = 0, выбирается режим 0 и когда D2 = 1, выбран режим 1.

- D5 & D6 используются для выбора режима группы A (порт A и верхний порт C). Выбор производится следующим образом:

| D6 | D5 | Режим |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | Икс | 2 |

- Поскольку это режим ввода / вывода, D7 = 1.

Например, если порт B и верхний порт C должны быть инициализированы как входные порты, а нижний порт C и порт A как выходные порты (все в режиме 0):

- Поскольку это режим ввода-вывода, D7 = 1.

- Все биты выбора режима, D2, D5, D6 равны 0 для режима 0.

- Порт B и верхний порт C должны работать как входные порты, следовательно, D1 = D3 = 1.

- Порт A и нижний порт C должны работать как выходные порты, следовательно, D4 = D0 = 0.

Следовательно, для желаемой операции регистр управляющего слова должен быть загружен "10001010" = 8A (шестнадцатеричное).

Режим 0 - простой ввод / вывод

В этом режиме порты могут использоваться для простых операций ввода-вывода без сигналов подтверждения. Порт A, порт B обеспечивают простую операцию ввода-вывода. Две половины порта C могут использоваться либо вместе как дополнительный 8-битный порт, либо как отдельные 4-битные порты. Поскольку две половины порта C независимы, их можно использовать так, что одна половина инициализируется как входной порт, а другая половина инициализируется как выходной порт.

Функции ввода / вывода в режиме 0 следующие:

- Выходные порты заблокированы.

- Входные порты буферизуются, а не фиксируются.

- Порты не поддерживают квитирование или прерывание.

- С 4 портами возможны 16 различных комбинаций ввода-вывода.

«С фиксацией» означает, что биты помещаются в регистр хранения (массив триггеров), который сохраняет свою выходную константу, даже если входы изменяются после фиксации.

Выходы 8255 фиксируются для хранения последних записанных на них данных. Это необходимо, поскольку данные остаются на шине только один цикл. Таким образом, без фиксации выходы станут недействительными, как только цикл записи завершится.

Входы не фиксируются, потому что ЦП должен только считывать их текущие значения, а затем сохранять данные в регистре ЦП или в памяти, если к ним нужно обратиться позже. Если вход изменяется во время чтения порта, результат может быть неопределенным.

Mode 0 - режим ввода

- В режиме ввода 8255 получает данные от внешних периферийных портов, а ЦП считывает полученные данные через свою шину данных.

- ЦП сначала выбирает микросхему 8255, делая CS низкий. Затем он выбирает желаемый порт с помощью A0 и А1 линий.

- Затем ЦП выдает Сигнал RD для чтения данных с внешнего периферийного устройства через системную шину данных.

Mode 0 - режим вывода

- В режиме вывода ЦП отправляет данные на 8255 через системную шину данных, а затем внешние периферийные порты получают эти данные через порт 8255.

- ЦП сначала выбирает чип 8255, делая CS низкий. Затем он выбирает желаемый порт с помощью A0 и А1 линий.

- Затем CPU выдает Сигнал WR для записи данных в выбранный порт через системную шину данных. Эти данные затем принимаются внешним периферийным устройством, подключенным к выбранному порту.

Режим 1 - Стробированный режим ввода / вывода

Когда мы хотим использовать порт A или порт B для операции ввода или вывода с квитированием (стробированием), мы инициализируем этот порт в режиме 1 (порт A и порт B могут быть инициализированы для работы в разных режимах, т.е., например, порт A может работают в режиме 0, а порт B - в режиме 1). Некоторые контакты порта C функционируют как линии подтверждения.

Для порта B в этом режиме (независимо от того, действует ли он как входной или выходной порт), контакты PC0, PC1 и PC2 функционируют как линии подтверждения.

Если порт A инициализирован как входной порт режима 1, то PC3, PC4 и PC5 функционируют как сигналы подтверждения. Контакты PC6 и PC7 доступны для использования в качестве линий ввода / вывода.

Режим 1, поддерживающий квитирование, имеет следующие особенности:

- Два порта, то есть порт A и B, могут использоваться как 8-битные порты ввода-вывода.

- Каждый порт использует три линии порта c в качестве сигнала подтверждения, а оставшиеся два сигнала могут использоваться как порты ввода-вывода.

- Поддерживается логика прерывания.

- Входные и выходные данные фиксируются.

Входные сигналы установления связи

- 1. IBF (входной буфер заполнен) - это выход, указывающий, что входная защелка содержит информацию.

- 2. STB (Strobed Input) - вход строба загружает данные в защелку порта, которая удерживает информацию до тех пор, пока она не будет введена в микропроцессор с помощью инструкции IN.

- 3. INTR (запрос прерывания) - это выход, который запрашивает прерывание. Вывод INTR становится логической 1, когда на входе STB возвращается логическая 1, и очищается, когда данные вводятся из порта микропроцессором.

- 4. INTE (разрешение прерывания) - не является ни входом, ни выходом; это внутренний бит, программируемый через битовую позицию порта PC4 (порт A) или PC2 (порт B).

Выходные сигналы подтверждения связи

- 1. OBF (выходной буфер заполнен) - это выходной сигнал, который становится низким, когда данные выводятся (OUT) на порт A или порт B. Этот сигнал устанавливается в логическую единицу всякий раз, когда импульс ACK возвращается от внешнего устройства.

- 2. ACK (подтверждение) - возвращает вывод OBF на уровень логической 1. Сигнал ACK - это ответ от внешнего устройства, указывающий, что оно получило данные из порта 82C55A.

- 3. INTR (запрос прерывания) - это сигнал, который часто прерывает микропроцессор, когда внешнее устройство получает данные через сигнал. этот вывод определяется внутренним битом INTE (разрешение прерывания).

- 4. INTE (разрешение прерывания) - не является ни входом, ни выходом; это внутренний бит, запрограммированный для включения или отключения вывода INTR. Бит INTE A программируется с помощью бита PC6, а INTE B - с помощью бита PC2.

Режим 2 - режим стробированного двунаправленного ввода / вывода

В этом режиме можно инициализировать только порт A. Порт A можно использовать для двунаправленное рукопожатие Передача данных. Это означает, что данные могут вводиться или выводиться на одних и тех же восьми линиях (PA0 - PA7). Контакты PC3 - PC7 используются в качестве линий подтверждения для порта A. Остальные контакты порта C (PC0 - PC2) могут использоваться в качестве линий ввода / вывода, если группа B инициализирована в режиме 0 или как подтверждение связи для порта B, если группа B выбрана. инициализирован в режиме 1. В этом режиме 8255 может использоваться для расширения системной шины до ведомого устройства. микропроцессор или для передачи байтов данных в и из дискета контроллер. Сигналы подтверждения и квитирования предоставляются для поддержания надлежащего потока данных и синхронизации между передатчиком и приемником данных.

Рекомендации

- ^ Р. Теагараджан (1 января 2004 г.). Микропроцессор и его применение. New Age International. С. 165–. ISBN 978-81-224-1040-2. Получено 3 июн 2012.

- ^ Программирование встроенных систем. Публикации Миллера Фримена. Июль 1996. с. 256. Получено 3 июн 2012.

- ^ "Страница продукта для 82C55A". Renesas Electronics. Получено 26 июля 2018.

- ^ Корпорация Intel, «Компонент микрокомпьютера: новая линейка продуктов промышленного уровня отвечает спросу на высоконадежные компоненты для работы в промышленных приложениях», Intel Preview, март / апрель 1979 г., стр. 11

- ^ Корпорация Intel, «Периферийные устройства Intel улучшают дизайн системы 8086», специальный выпуск Intel Preview: 16-разрядное решение, май / июнь 1980 г., стр. 22

- ^ Роберт Журден (1986). Решение проблем программиста для IBM PC, XT и AT. Brady Communications Co. стр. 3. Получено 3 июн 2012.

- ^ Мир электроники. Reed Business Pub. 1996. стр. 947. Получено 3 июн 2012.

- ^ «Техническое описание Intel 82c55 PPI» (PDF).

- ^ "Спецификация PCI 82C55A" (PDF).

- ^ Байт. Макгроу-Хилл. 1981. с. 40. Получено 3 июн 2012.

- ^ U. S. Shah. «11». Микропроцессор и методы сопряжения (второе изд.). Публикация Techmax. С. 11–5. ISBN 978-81-8492-305-6.

- ^ "Введение в i8255" (PDF).

внешняя ссылка

- drew.hickmans.net, Полное описание микросхемы Intel 8255

- ic-on-line.cn, Техническая спецификация

- sharpmz.org, обзор функций

- intel-assembler.it, Технические детали программирования и пример кодирования

- bitsavers.informatik.uni-stuttgart.de, Руководство пользователя микрокомпьютерных систем Intel 8080 (сентябрь 1975 г.). Включает чип 8255.